# Modeling and Evaluation of Cache Coherence Mechanisms for Multicore Processors

نمذجة وتقييم طرق تماسكية الذاكرة المخبئة في المعالجات متعددة الأنوية

by

## Malik Amin Mohammad Al-Manasia

Supervisor

Dr. Faruq Al-Omari

Co-Supervisor

Dr. Mohammad Al-Jarrah

Program: Industrial Automation Engineering

# Modeling and Evaluation of Cache Coherence Mechanisms for Multicore Processors

by

## Malik Amin Mohammad Al-Manasia

B.Sc. Computer Engineering, Mutah University, 2008

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in the Department of Computer Engineering, Yarmouk University, Irbid, Jordan

| Approved by:                                                    |         |

|-----------------------------------------------------------------|---------|

| Faruq A. Al-Omari C                                             | hairman |

| Associate Professor of Computer Engineering, Yarmouk University |         |

| Salem Y. Al-Agtash                                              | ember   |

| Associate Professor of Computer Engineering. Yarmouk University |         |

| Hussien R. Al zoubi H: Al zoubi M                               | ember   |

| Assistant Professor of Computer Engineering, Yarmouk University |         |

| Emad M. Shawakfa                                                | lember  |

April 17, 2011

## **ACKNOWLEDGMENTS**

Thank God that I have received a lot of help and support from many people over the past few months. I cannot imagine making it this far without such support. I am deeply grateful to my supervisors, Dr. Faruq Al-Omari and Dr. Mohammad Al-Jarrah. They have been outstanding mentors who provided me with a lot of support and guidance. I have learned a lot under their supervision. I am thankful that they gave me as much of their time as I asked for, and provided me with support when I needed it the most.

My research required many hours of simulation time, and I would like to acknowledge those who helped made it possible. I thank Virtutech AB and Wind River "the companies that support the Simics simulator which we used in the scope of this thesis" for answering many of my technical questions. I would also like to thank the Condor project from Wisconsin University for their support.

My heartfelt thanks go to my mother, to my father, to my siblings, and to my friends. This work could not have been accomplished without their support.

April 2011

# TABLE OF CONTENTS

| Table of Contents                                                    | <u>Page</u> |

|----------------------------------------------------------------------|-------------|

|                                                                      | E CO        |

| ACKNOWLEDGMENTS                                                      | II          |

| TABLE OF CONTENTS                                                    | III         |

| LIST OF TABLES                                                       | VI          |

| LIST OF FIGURES                                                      | VII         |

| ABSTRACT (in English)                                                | VIII        |

| ABSTRACT (in Arabic)                                                 | IX          |

| Chapter 1 Introduction                                               | 1           |

| 1.1 Cache Coherence and Multicore                                    | 1           |

| 1.2 Desirable Cache Coherence Attributes                             | 5           |

| 1.3 Thesis Structure                                                 | 9           |

| Chapter 2 Background and Motivation                                  | 10          |

| 2.1 Multicore Architectures                                          |             |

| 2.1.2 Multicore Challenges                                           | 11          |

| 2.1.3 Multicore processor vs. Multiprocessors                        | 13          |

| 2.1.4 Multicore Commercial examples                                  | 14          |

| 2.2 Memory Caching in Multicore Systems                              | 14          |

| 2.2.1 Cache necessity and it's work principle                        |             |

| 2.2.2 Private vs. Shared caches                                      | 16          |

| 2.3 Cache Coherence Protocols      2.3.1 The cache coherence problem |             |

| 2.3.2 Basic Operation of Cache Coherence Protocols                   | 20          |

| 2.3.3 Hardware Protocols                                             | 24          |

| 2.3.3.1 Snoop Bus Protocols                                          | 24          |

| 2.3.3.2 Directory-Based Protocols                                    | 24          |

| 2.3.3.3 Token Protocols                                              | 25          |

| 2.3.4 Compiler and Software protocols                                | 25          |

| 2.3.4.1 Software Coherence with Limited Hardware Support        | 26 |

|-----------------------------------------------------------------|----|

| 2.3.4.2 Enforcing coherence by Restricting Parallelism          | 27 |

| 2.3.4.3 Optimizing Compilers                                    | 27 |

| 2.4 Literature Review and Related work                          | 27 |

| Chapter 3 Evaluation Methodology                                | 30 |

| 3.1 Simulation Tools                                            |    |

| 3.1.2 Ruby Module                                               | 32 |

| 3.2 Performance Metrics                                         | 32 |

| 3.3 Workload Descriptions                                       | 34 |

| 3.4 Modeling a CMP with Simics/GEMS                             |    |

| 3.4.2 Coherence Protocols                                       | 37 |

| 3.4.3 System Interconnects                                      | 38 |

| Chapter 4 Cache Coherence Protocols                             | 39 |

| 4.1 Snooping Protocols                                          |    |

| 4.1.2 Advantages of Snooping Protocols                          | 44 |

| 4.1.3 Disadvantages of Snooping Protocols                       | 45 |

| 4.1.4 Techniques used to improve Snoopy based Cache Coherency   | 46 |

| 4.1.5 Implementing Snoopy Cache Coherence                       | 47 |

| 4.1.5.1 Basic Implementation Techniques                         | 47 |

| 4.1.5.2 The proposed Snooping Protocol Implementation: SNOOPING | 49 |

| 4.2 Directory-based Protocols                                   |    |

| 4.2.2 Advantages of Directory Protocols                         | 56 |

| 4.2.3 Disadvantages of Directory Protocols                      | 57 |

| 4.2.4 Techniques used to improve directory based protocol       | 58 |

| 4.2.4 The proposed Directory Protocol Implementation: DIRECTORY | 60 |

| 4.3 Token-based Protocols                                       |    |

| 4.3.2 Ramifications on design verification                      |    |

|                                                                 |    |

| 4.3.3Token Operation and Implementation                   | 65   |

|-----------------------------------------------------------|------|

| 4.3.4 TokenB Coherence Example                            | .68  |

| 4.4 Simulation Results                                    | . 69 |

| Chapter 5 Analysis and Evaluations                        | .72  |

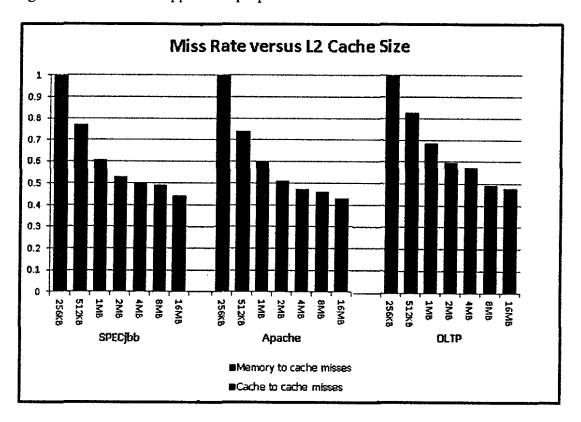

| 5.1 Memory-to-Cache and Cache-to-Cache Misses             |      |

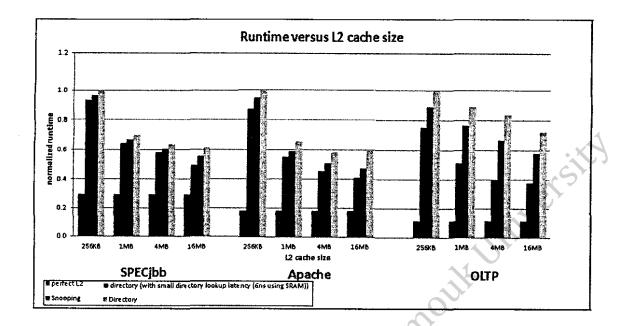

| 5.2 Indirection and its Effects on Performance.           | . 75 |

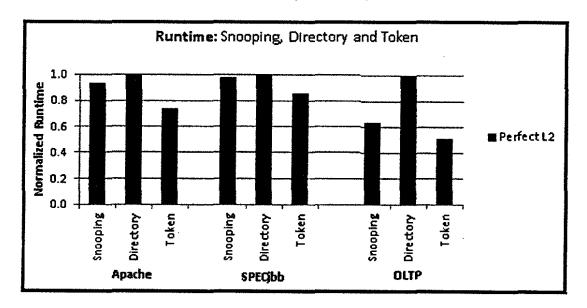

| 5.3 TOKENB versus Snooping                                | . 77 |

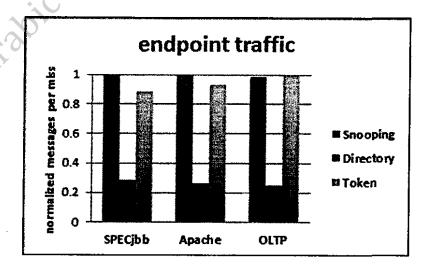

| 5.3 TOKENB versus SNOOPING                                | 79   |

| Chapter 6 Conclusions and Recommendations for Future Work | 81   |

| 6.1 Conclusions                                           | 81   |

| 6.2 Recommendations for Future Work                       | 82   |

| REFERENCESAPPENDECES                                      | 83   |

| APPENDECES                                                | 97   |

| Appendix 1: ABBREVIATIONS                                 | 97   |

| © Arabic Digital                                          |      |

## LIST OF TABLES

| Tables    |                                      | Page |

|-----------|--------------------------------------|------|

| Table 2.1 | MOESI State Transitions              | 23   |

| Table 3.1 | Simulation Parameters                | 37   |

| Table 4.1 | Snooping Coherence Protocol Results  | 69   |

| Table 4.2 | Directory Coherence Protocol Results | 70   |

| Table 4.3 | TOKENB Coherence Protocol Results    | 70   |

# LIST OF FIGURES

| Figures    |                                                           | Page |

|------------|-----------------------------------------------------------|------|

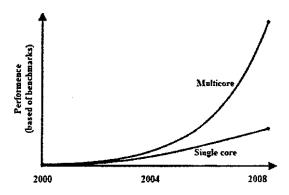

| Figure 1.1 | Multi core performance compared to single core            | 1    |

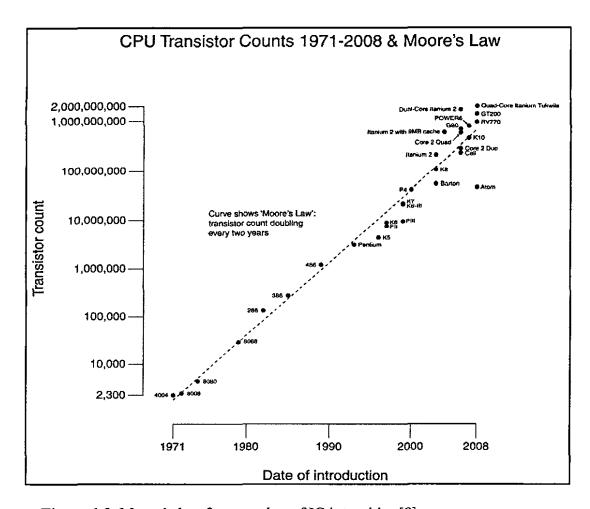

| Figure 1.2 | Moore's law for number of IC intensity                    | 3    |

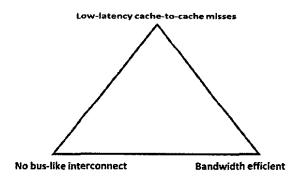

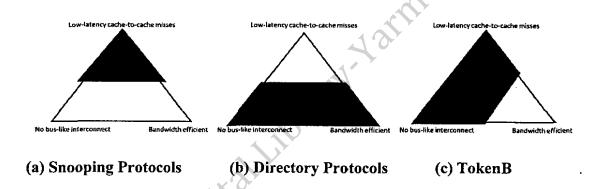

| Figure 1.3 | Characterizing Common Protocols in Terms of Three         |      |

|            | Desirable Attributes                                      | 8    |

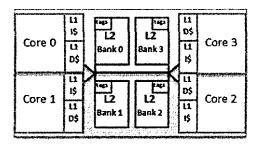

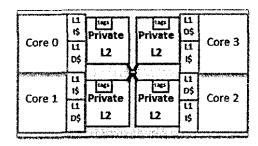

| Figure 2.1 | CMP Shared and Private L2 Caches                          | 17   |

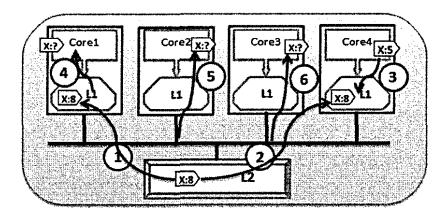

| Figure 2.2 | Cache Coherence Problem                                   | 19   |

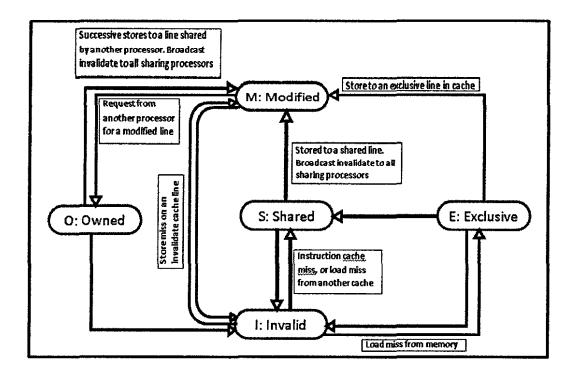

| Figure 2.3 | The basic operations of MOESI states                      | 23   |

| Figure 3.1 | A view of the GEMS architecture with simics simulator     | 31   |

| Figure 4.1 | Snooping Process                                          | 39   |

| Figure 4.2 | An example of an invalidation protocol working on a       | L    |

|            | snooping bus for a single cache block (X) with write-back | :    |

| Ô          | caches                                                    | 44   |

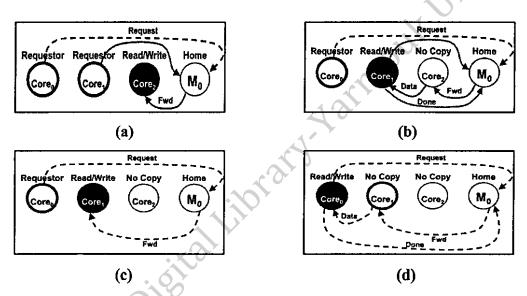

| Figure 4.3 | Directory based protocol example                          | 52   |

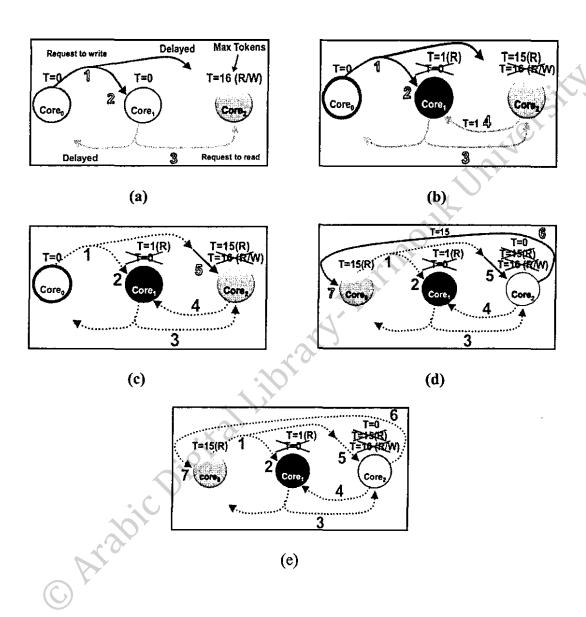

| Figure 4.4 | Token based protocol example                              | 68   |

| Figure 5.1 | Miss Rate vs. Cache Size.                                 | 73   |

| Figure 5.2 | Runtime vs. Cache Size                                    | 76   |

| Figure 5.3 | Runtime of Snooping, Directory, and TOKENB                | 77   |

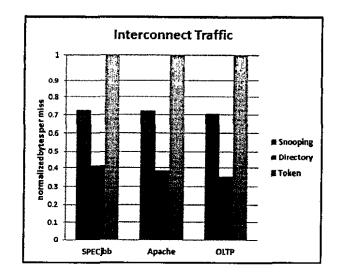

| Figure 5.4 | Endpoint Traffic of Snooping, Directory, and TOKENB       | 78   |

| Figure 5.5 | Interconnect Traffic of Snooping, Directory, and TOKENB   | 79   |

|            |                                                           |      |

## **ABSTRACT**

Almanasia, Malik Amin. Modeling and Evaluation of Cache Coherence Mechanisms for Multicore Processors. Master of Science Thesis, Department of Computer Engineering, Yarmouk University, 2011 (Supervisor: Dr. Faruq Al-Omari and Dr. Mohammad Al-Jarrah).

Multiple core designs have become commonplace in the processor marketplace, and are therefore a major focus in modern computer architecture research. Thus, for both product development and research, multiple core processor performance evaluation is a mandatory step in marketplace. A well-known positive feedback property of computer design is that we use computers of today to design more powerful computers for the future. Thus, with the appearance of Chip Multi-Processors (CMP), it is more natural to take advantage of its efficiency.

Multicore computing have presented many challenges for system designers; one of which is data consistency between a shared cache or memory and the local caches of the chip. This is also known as cache coherency. The cache coherence mechanisms are a key component in the direction of accomplishing the goal of continuing exponential performance growth through widespread thread-level parallelism.

In the scope of this research, we have studied the available efficient methods and protocols used to achieve cache coherence in multicore architectures. These protocols were further modeled and evaluated utilizing simics simulator for multicore architectures. We also investigated the weaknesses and strengths of different protocols and discussed the way of improving them.

**Key Words**: Cache Coherence Protocols, Multicore, Snooping, Directory, Token.

## الملخص

المناسيه، مالك أمين. نمذجة وتقييم طرق تماسكية الذاكرة المخبنه في المعالجات متعددة الأنويه. رسالة ماجستير بجامعة اليرموك. 2011. (المشرف: د.فاروق العمري، المشرف المشارك: د.محمد الجراح)

أصبحت المعالجات متعددة الأنوية منتشرة بشكل واضح في الأسواق، وأصبح هناك تركيز على أبحاث هيكلية الحاسوب الحديثة. ولتطوير هذا المنتج والأبحاث المتعلقة به صار من الضروري إجراء تقييم أداء للمعالجات متعددة الأنوية لنسير خطوة نحو الأمام. ولحسن الحظ انه يمكننا الإستفادة من الحواسيب العالية الآداء حاليا لإنتاج حواسيب أفضل آداء للمستقبل.

قدمت الأنظمة متعددة الأنوية عدد من التحديات لمصممي الأنظمة، وتعتبر تماسكية وترابط البيانات بين الذاكرة المخبئة المشتركة او الذاكرة الرئيسية و الذاكرة المخبئة المحلية احد أهم هذه التحديات. يؤدي تحقيق هذا للوصول الى زيادة كبيرة في الآداء والى الاستفادة من العمليات المتوازية بشكل أفضل.

في نطاق هذه الرسالة قمنا بدراسة الطرق والبروتوكولات الأكثر فاعلية لتحقيق تماسكية الذاكرة المخبئة في المعالجات متعددة الأنوية. قمنا بنمذجة وتقييم هذه البروتوكولات باستخدام أحد أفضل برامج المحاكاة المتوفرة يسمى simics. ايضا قمنا ببحث ودراسة نقاط الضعف والقوة لكل هذه البروتوكولات وكيفية جعلها أفضل.

الكلمات المفتاحية: تماسكية الذاكرة المخبئة، المعالجات متعددة الأنوية.

## **Chapter 1 Introduction**

Four Intel Corporation technologists have established multicore processors to come to market after the turn of the 20<sup>th</sup> century, who forecasted the future through the lens of Moore's Law. This was in the 1989 issue of IEEE Spectrum, an article entitled "Microprocessors Circa 2000" [1]. After fifteen years their predictions are verifying true and multicore processor capability development have turned out to be one of the top business and product initiatives for Intel and other companies.

## 1.1 Cache Coherence and Multicore

There is a great correlation between power and processor clock rate. When the clock rate is enhanced, the power will also rise; after which, the temperatures will also increase [2]. Multicore processors take advantage of this relationship by combining multiple cores. Each core is able to run at a lower frequency. By splitting up the power "provided to a single core" normally between all cores [3], the performance will enhance, whereas the power and temperatures are still under control. Figure 1.1 shows this main advantage and the significant performance enhancement over the single core processor [2, 4].

Figure 1.1 Multi core performance compared to single core.[2]

Also, multicore technology can improve system efficiency and application performance for computers running multiple applications and multi-threaded programs simultaneously [5, 6].

Computing has revolutionized society and worked as an engine of the world's economy. Much of this revolution is the result of the advent and incredible progress of the low-cost microprocessor [7].

Enhancement of microprocessors is guided greatly by Moore's Law, which has forecasted that the number of transistors per silicon area will double every eighteen months [8]. Computer architects are embarking on a fundamental shift in how the transistor bounty is used to increase performance, while Moore's Law is expected to continue at least into the next decade [111]. Figure 1.2 illustrates the transistor count has been doubling every two years.

Regarding multicore processors, cache coherency stands for the credibility of data stored in each core's cache. Multicore processors may contain distributed and shared caches on the chip, so we should account for the coherence protocols to assure that when a core reads from memory, it reads the current piece of data and not a value that has been updated by a different core.

Figure 1.2. Moore's law for a number of IC intensities [8].

Cache coherence is considered to be one of the most important dilemmas in a multicore environment due to distributed Level1(L1) and sometimes Level2 (L2) caches. The copy of the data in any cache may not always be the most recent version, as each core has its own cache. For example, consider a quad-core processor where each core fetched a certain block of memory into its private cache. One core writes a value to a specific location; when the second core tries to read that value from its cache, it might not have the updated copy unless its cache entry is invalidated and a cache miss occurs. This cache miss forces the updating of the other core's cache entry. If this coherence policy wasn't present, garbage data would be read and invalid results would be produced, this may lead to crashing the program or the entire system.

There are two ways to deal with the cache coherency problems.

- Software Cache Coherence Schemes.

- Hardware Cache Coherence Schemes.

In the Software-Based Coherence, which is a straightforward method, shared data are not cached [9]; this can be made by the operating system, the compiler, or the programmer.

Hardware-Based Coherence is one, which is enforced by snoop devices attached to the cores and their caches. In this scheme, because caches are guaranteed to be coherent, shared data can be cached, but a programmer must deal with the synchronization of shared data [9].

In hardware-based cache coherency, there are in general two methods, a snooping protocol and a directory-based protocol. The Snoopy cache-coherence methods require sending information to all of cache controllers. However, if the number of cores increases the cache messages will also increase, then the required bus, "which connect the caches and all messages will pass through it", bandwidth will be bigger than the available one, and then a total saturation of the bus bandwidth would occur. These techniques can be used in small-scale systems due to this limitation.

On the other hand, the Directory-based protocol will scale to larger number of processors or cores than the snoopy-based coherence protocol, since it enables multiple coherence actions to take place at the same time [9].

Over the last 10 years, much work have been done to enhance cache coherency performance, this has resulted in a number of new cache coherency protocols. Token coherence protocol, is one of the most efficient new protocols.

The recently suggested Token coherence protocol [10, 11, 12] can remove the constraint of directory indirection without sacrificing either the decoupling of the

interconnection from the coherence protocol or the decoupling of coherence from consistency. To resolve races without asking for a home node or an ordered interconnection; Token coherence uses token counting. As will be discussed in details in chapter four.

## 1.2 Desirable Cache Coherence Attributes

There are three critical attributes that have an impact on the performance of any cache coherence protocol:

#### 1. Low-latency Cache-to-Cache Misses

Many commercial workloads exhibit abundant thread-level parallelism, and thus, using multiple processors or cores is a desirable method for enhancing their performance [11]. To efficiently support the frequent communication and synchronization in these workloads, systems are required to optimize the latency of cache-to-cache misses [13]. A cache-to-cache miss is a miss frequently caused by accessing shared data that requires another processor's cache to provide that data. To decrease the latency of cache-to-cache misses, a coherence protocol should ideally support direct cache-to-cache misses. For example, snooping protocols support fast cache-to-cache misses by broadcasting all requests to find the responder directly. On the contrary, by placing a directory lookup and a third interconnect traversal on the critical path of cache-to-cache misses, directory protocols indirectly locate remote data.

#### 2. No Reliance on a Bus or Bus-like Interconnect

Unfortunately, snooping protocols depend on a bus or bus-like interconnect to enable their fast cache-to-cache transfers. Such interconnects are not as good as with two important technology trends: high-speed point-to-point links and increasing levels of integration. As discussed below shortly, creating a bus-like or "virtual bus"

interconnect demands it to give a total order of requests [11]. An interconnect gives a total order if all messages are delivered to all destinations in some order. A total order demands an ordering between all the messages (even those from different sources or sent to different destinations). For example, if any processor receives message A before message B, then no processor receives message B before A. Unluckily, creating a totally-ordered interconnect that uses both of the two important technology trends described below is infeasible using the traditional techniques. Because of that, protocols depending on a totally-ordered interconnect—such as snooping protocols— are unattractive, and protocols that do not depend on such an interconnect—such as most directory protocols—are more desirable [11].

## - High-speed point-to-point links.

Continued scaling of the bandwidth of shared-wire buses is hard due to electrical implementation realities [14]. To overcome this limitation, some multiprocessor systems replace shared-wire buses with high-speed point-to-point links that can provide considerably more bandwidth per pin than shared-wire buses [15]. Many recent snooping protocols use virtual bus switched interconnects that exploit high-speed point-to-point links, even though; many early snooping systems depended on shared-wire buses. These interconnects provide the bus-like ordering properties necessary for snooping, often by ordering all requests at the root switch chip.

#### - Higher levels of integration.

Moore's Law predicted enhanced number of transistors per chip, this has encouraged, and will continue to encourage, more integrated designs, making "glue" logic (e.g., dedicated switch chips) less desirable. Many systems integrate processor(s), cache(s), coherence logic, switch logic, and memory controller(s) on a single die (e.g.,

AMD's Hammer [16]). Connecting these highly-integrated nodes directly leads to a high bandwidth, low-cost, low-latency "glueless" interconnect [11].

## 3. Bandwidth Efficiency

Bandwidth efficiency is the third—and almost the least important at the time—required attribute [11]. A cache coherence protocol should conserve bandwidth to decrease the cost and avoid interconnect contention (since contention reduces performance), but a protocol should not sacrifice any of the first two attributes for the sake of obtaining this less-important third attribute. For example, an essay estimated that, less than 10 systems contained 256 or more processors (~ 0.03%) of the 30,000 Origin 200/2000<sup>1</sup> [17] systems shipped, and less than 250 of the systems had 128 processors or more (~ 1%) [11]. No new multicore processors exceeded one hundred cores per chip [18].

As exhibited in Figure 1.3, neither predominant approach to coherence captures all three of these attributes: two are captured by directory protocols and TokenB while one is captured by snooping.

Figure 1.3 exhibits the three required properties described in this section and which of these attributes are supported by snooping (part a), directory protocols (part b), and TokenB protocol (part c). Each triangle stands for a different protocol, and each vertex accounts for a different attribute. The shaded portions of the triangle exhibits the attributes illustrated by the corresponding protocol. As illustrated in this figure, the set of these desirable attributes captured by snooping, directory, and Token protocols is disjoint, because of that, neither protocol has all the required properties.

<sup>&</sup>lt;sup>1</sup> Origin 2000, code named *Lego*, is a family of mid-range and high-end servers developed and manufactured by SGI (Silicon Graphics, Inc.).

## Three desirable Attributes

Figure 1.3 Characterizing Common Protocols in Terms of Three characteristics [11].

Token-using-Broadcast (TOKENB) performance policy aims at capturing 1) Low-latency Cache-to-cache Misses and 2) No Reliance on a Bus or Bus-like Interconnect at the same time (i.e., avoid an ordered interconnect and provide low-latency cache-to-cache misses). These two attributes are the most important of the three attributes, and aiming at both of these attributes results in a low-latency, broadcast-based coherence protocol that is suitable for applications with a glueless, point-to-point interconnect.

## 1.3 Thesis Structure

This thesis begins with introductory chapter (Chapter 1) and continues with a chapter that describes the fundamentals and background about multicore architecture and memory caching (Chapter 2). We then describe and discusses the tools, methodology, and workloads used for the evaluation and simulation of different systems (Chapter 3) and continues with a chapter that describes the traditional cache coherence protocols (Directory and snooping) in addition to TokenB protocol (Chapter 4). And then we evaluate each protocol and discuss the results (Chapter 5). The thesis ends with chapter 6 which concludes our work and gives directions for the future work.

## **Chapter 2 Background and Motivation**

## 2.1 Multicore Architectures

Chip Multiprocessor [19,20,21] refers to the technique of summing the power of more than one core on one chip or die. The process of connecting multiple-cores is done over a packet-based or bus-based network. Chip manufacturers are tending to concentrate on the production of multicore chips, as their architectures allow the computing of a number of tasks at the same time thus, enhancing the performance of the system [22,23,24].

As the world is evolving into a more digitalized pattern and the constant growth of performance, multicore architectures are presenting the computing technology with a key development. Multicore architectures will prevail as the predominant computing model for, they far exceed the performance and productivity benefits of single-core processors.

## 2.1.1 Multicore Necessity

Numerous new applications are becoming multithreaded and the computer architecture is turning its focus toward parallelism. This is because it is very hard to enhance the performance of single core processors by increasing the clock frequencies, let alone the probable difficulties such as heating or speed of light, if the frequency exceeds certain ranges, the design and verification needs a large team as well.

The usage of packet based on-chip networks decreases the power dispersion so that it provides the ability for other cores to operate (although in a decreasing fashion). If one core fails, for they are completely independent, Multicore Architecture allows for hardware scalability and escalades software scalability [25]. Multicore Architecture also supports hardware reuse thus, helping in decreasing time-to-market, increasing the productivity and diminishing the cost [26].

The cache coherency circuitry functions at a much higher clock rate performed over multiple CPU cores on the die than when signals travel off-chip.

The cache snoop operations are highly improved by combining counterpart CPUs on a single die. By this, we mean that signals travel a shorter distance between variant CPUs as so the signals will degrade less. The finer quality of signals allow for more data sending in a given period of time as individual signals do not need duplication.

Multicore design makes best usage of the silicon die area; baring in mind that the availability of the silicon substance is insufficient for the demand, thus, by using proven core library designs to come up with minimal design errors compared to devising a new wider core design. Adding additional cache as well produces the disadvantage of diminishing returns [27].

#### 2.1.2 Multicore Challenges

Multicore design is faced with many challenges, like any new design. These challenges require identification and understanding. One of the main challenges facing Chip Multiprocessors (CMPs) is the competition for shared resources. This challenge forms a restriction bottleneck [28,29,30]. Some of the shared resources are: main memory, bandwidth and capacity, cache bandwidth and capacity, memory subsystem interconnection bandwidth, and system power. Listed below are the main challenges:

Multicore architecture might escalade the complexity for designers and developers

for its parallel architecture of hardware and software. It is easier to manage lower

density single-chip designs' conduction of heat compared to multicore chips that

on their turn, generate lower returns on production [26].

The architectural perspective concludes that a better usage of the silicon surface area is obtained by single CPU designs, not multiprocessing core, risking the extent of the development dedicated to this particular architecture. Last but not least; raw processing power is the only, but one of, the obstacles facing system performance. The real world performance advantage is constrained by sharing the same system bus and memory bandwidth between the two processing cores. Dual core improvement is limited between 30% and 70% if a single core is close to being memory bandwidth limited, On the other hand, an improvement of 90% is expected if memory bandwidth is not an issue. More than 100% improvement is accounted if an application that used two CPUs operated at a faster level on dual core due to the limiting factors in communication between the CPUs [27].

- 2. The concurrency principles are not fully accustomed by today's designers, developers, and test engineers. These principles are difficult to absorb and, as a result, the time for product development is increased as the development teams will have to be retrained [31]. Existing software modifications are mandatory as well as operating system support (OS). Moreover, multicore processors' ability to enhance application software performance is bound to the application usage of multiple threads. For example, a present-day PC operates faster on a 3 GHz single-core processor than on a 2 GHz dual core (of the same core architecture), regardless of the theoretical assumption that dual-core processors obtain more processing power, because of their incapability of seizing more than one core at a time in an efficient manner.

- 3. Many issues need to be considered by developers like Processor synchronization, latency, and speed gap, Bandwidth requirements, while transmitting data over network, and program partitioning issues [32].

4. Throughout a debugging session; deadlocks, livelocks, and data corruption are difficult to trace, as they are discontinuous. Furthermore, the pluralities of the current high-level languages are non-supportive for concurrent programming.

#### 2.1.3 Multicore processor vs. Multiprocessors

Multicore processor derives from the family of multiprocessors with the significant difference of the gathering of all the processors on the same chip. Compared to multiprocessors, multicore processor is a better option for its low design complexity, high clock frequency, and high throughput.

Multicore processors differ for their Multiple Instructions Multiple Data (MIMD) as the various cores execute different threads (Multiple Instructions), operating on multiple parts of memory (Multiple Data). In fact, the same memory is shared among all cores as so, multicore is a shared memory multiprocessor.

While multi processors are multiple chips that are plugged into the motherboard and therefore allocate an unshared cache for each chip, multicore processors have more than one core with the ability to execute processing on one chip, normally by allocating an unshared L1 cache for each core and the sharing of L2 and/or L3 caches.

Communication of data among processors in the current shared-memory multiprocessors may vary from 50 clock cycles (for multicores) to more than 1000 clock cycles (for large-scale multiprocessors) thus, affected by the communication mechanism, the type of interconnection network, and the scale of the multiprocessor. The impact of such delay in long communications is of obvious significance [33].

Multiprocessors contain one large and fast superscalar core that performs greatly on a single thread, although, still exploits instruction level parallelism exclusively. On the other hand multicore obtain many cores each is smaller comparatively less powerful

(although easier to design and manufacture) still, highly capable with thread level parallelism.

The multicore CPU uses a smaller Printed Circuit Board (PCB) than multi-chip SMP designs that, if we hypothetically assumed that the die can be physically placed in the package. Moreover, the power consumption of a dual-core processor is somewhat less than two single-core processors combined; hence, the power needed to drive signals external to the chip, and as cores are able to operate at lower voltages on a less silicon process geometry, as a result to such reduction, the latency is reduced. Furthermore, some circuitry is shared between cores such as: the L2 cache and the interface to the front side bus (FSB) [34,35].

## 2.1.4 Multicore Commercial examples

The first on-chip multiprocessor for the computing market of the general purpose was presented in the year 2000 by IBM. Followed in the year 2005 by AMD that presented the two processor versions for the server market. In the end of the year 2007 and early 2008, the kickoff quad-core and triple-core processors were introduced, whereas an 8-core chip for computer-farm application was produced by Sun in 2006. On the 20th of August 2007 however, Tilera gave off its 64-core processor.

Intel also released its two-processor versions in 2005 for the server market; its quad core processor was presented on Dec 13, 2006. Within the coming years, Intel is expected to release its 80-core processor prototype, each running at 3.16GHz[36].

## 2.2 Memory Caching in Multicore Systems

Cache memory is defined as a specific memory subsystem whereas data of persistent usage is stored for fast access. The frequently accessed upper memory level locations and addresses of the data items are stored in the memory cache. The cache checks to see if the addresses referenced by the processor in memory are held in that address, so that if they are, the data is returned to the processor, if not; an ordinary memory access takes place. A cache is of use when microprocessors' speed exceeds the RAM accesses' speed, for cache memory is ever faster than main RAM memory [32].

Memory cache levels are divided into three types: 1) Level 1 cache (L1) is a small, fast memory cache contained in each core as it helps increase the access speed to the frequently-used data; 2) Level 2 cache (L2) is of a bigger size than L1 and is built into the microprocessor chip and occasionally between the microprocessor and the main memory; and 3) Level 3 cache (L3) is a combination of fast, built-in memory chips located between the microprocessor and the main memory, although not found in all MA designs[37].

## 2.2.1 Cache necessity and it's work principle

At this point, a question is raised "Why can't we speed up the entire computer's memory to match the speed of the L1 cache, and therefore eliminate the need for cache memory?" The answer to such question would be: speeding up the entire memory is a reasonable solution, but it would be extremely expensive. Caching is used to increase the speed of large amounts of slow, affordable memory by using a small amount of expensive memory [38].

The goal of designing a computer is to permit the microprocessor to run at its most speed with the least cost possible. A 500-MHz chip runs 500 million cycles per second (one cycle every two nanoseconds). The main memory would need 60 nanoseconds, or we would waste 30 cycles in accessing the memory without the usage of L1 and L2 caches [38].

It is somewhat astonishing that such comparatively micro amounts of memory allows for the magnification of much larger amounts of memory. Consider an L2 cache

of 256-kilobytes enabling the caching of 64 megabytes of RAM. If so, 64, 000, 000 bytes are cached efficiently using 256, 000 bytes [38]. This is justified by the computer science principle "locality of reference", Indicating that only small portions of a code is mostly used at the same time, even with great programs of several megabytes of instructions. Programs often spend large periods of time repeatedly working in one small area of the code, mostly repeating the same work many times redundantly with barely any different data, shifting afterwards to a different area. "Loops" are the reason behind this, as they are what programs use in order to work many times in rapid succession [39].

The cache is programmed (in hardware) to save the recently-accessed memory locations in case of later necessity. After being loaded for the first time from the memory, instructions are saved in the cache. Next time the instructions are needed, the processor checks the cache first, to see if the needed instructions are available, and directly loads these instructions from cache and not from the slower system components; RAM. The function of the caches design and size are what determines the number of instructions buffered by this method.

## 2.2.2 Private vs. Shared caches

Shared L2 caches are used by a group of CMPs in order to magnify the on-chip cache capacity and to minimize off-chip misses. Some use private L2 caches as to replicate data in order to limit the delay caused by global wires and to minimize cache access time. However, recent hybrid proposals balance latency and capacity using selective replication, on the other hand, their static replication rules cause a degradation in performance for some combinations of workloads and system configurations [40].

The occurrence of Chip Multiprocessors in mainstream systems forces them to provide a variety of workloads with a reasonable performance. In order to confront the interfering requests of reducing off-chip misses (capacity) and handling slow global wires (latency) in particular, Level-2 (L2) cache management brings forward a main challenge. The IBM Power 5 [41] and Dun Niagara [42] of the existing CMP systems use shared L2 caches (Figure 2.1a illustrates shared caches in CMP) to prevent replication in order to maximize the on-chip capacity. Although the cross global wires to reach distant L2 banks, many requests causes them to have higher access latencies. In contrast, private L2 caches (Figure 2.1b illustrates private caches in CMP), reduce average access latency by replicating data close to the requesting core, but sacrifice effective capacity and incur more misses [43,44].

- a) Layout of CMP-Shared L2

- b) Layout of CMP-Private L2

Figure 2.1 CMP Shared and Private L2 Caches.

## 2.3 Cache Coherence Protocols

#### 2.3.1 The cache coherence problem

Storing frequently accessed data in faster memory caches provide a more enhanced performance. More than one core is enabled to cache an address (or data item) simultaneously being that the same address space is shared by all cores. Although, many other elements of great importance are to be taken into consideration when using cache memory in a multicore environment, to be precise, preserving the right copies of data in all caches in the system. Inconsistencies can occur and incorrect executions may take

place as a result of updating a data item by a single processor without informing the remaining processors.

More than one copy of the same data may be kept by multiple caches in a multicore system; therefore, inconsistency between caches may take place as well as inconsistency between the main memory or upper cache levels and the private cache. A complication only exists if individual processors alter their copies of data, because shared data copies should be kept identical for correct operation. Maintaining the data in all the caches the same is known as cache coherence. The phrase cache consistency is also used.

The cache coherence problem is illustrated in Figure 2.2, which illustrates a shared L2 cache by four cores with private caches via a bus. The cores access location X sequentially. At the beginning, core1 brings a copy to its cache by reading X from L2 cache. After that, core 4 brings a copy to its cache by reading X from L2 cache. Thereafter core 4 changes X's location value from 8 to 5. With a write-through cache, causing the L2 cache location to be updated, but in (action 4) when core1 reads location X again, it will read the old value 8 from its own cache rather than reading its correct value 5 from L2 cache.

The writeback caches complicates the situation even further. Core4's write would not update L2 cache right away; instead, it would barely set the dirty (or modified) bit concerned with the cache block holding location X. Contents of cache block would be written back to L2 cache solely, when this cache block is subsequently replaced from the cache of core 4. The reading of the old value is not inclusive to core1. Furthermore, core2 and core3 will miss in their caches when reading location X (actions 5 and 6) by reading the old value 8 instead of 5 from L2 cache. Last but not least, if more than one core write different values in their write-back caches to location X, the last value that

will reach the L2 cache will not be related to the sequence in which the writes to X occurred. Instead, it will be determined by the sequence in which the cache blocks that contain X are replaced.

Figure 2.2 cache coherence problem

Coherence between the caches has to be enforced in order for correct execution. This process is affected by two main factors: Performance and implementation costs. In the process of designing a cache coherence mechanism, four main issues must be taken into consideration as well: 1) Coherence detection strategy- How possible incoherent memory access is detected by the system, 2) Coherence enforcement strategy- How to change cache entries in order to assure coherence (i.e. Updating or invalidating), 3) Precision of block sharing information- How sharing information and cache and memory blocks are stored and cache block size, and finally 4) the size of line in the cache and how the performance of the system is affected by it [45].

The cache coherence protocol comprises an absolute design choice for multicore and multiprocessor systems as it directly influences the overall system performance. Many system elements can influence the general performance to various certain levels thus reckon the selection of coherence protocols and the target application workloads, some of which are: the maximum achievable bandwidth (in snoop-based protocols) and network transactions number (in directory based protocols). Thorough evaluations over

the past decades have been made on the coherence of protocols since their commencement.

## 2.3.2 Basic Operation of Cache Coherence Protocols

In order to assure coherence invariant, coherence protocols track read and write permissions of clocks held by processor cores caches by using the protocol states. The states providing a set of common states in for reasoning about cache coherence protocols are described in this section, most common protocols apply these states such as MSI (Modified, Shared, and Invalid), MESI (Modified, Exclusive, Shared, and Invalid), MOSI (Modified, Owned, Shared and Invalid) and MOESI (Modified, Owned, Exclusive, Shared, and Invalid).

Firstly; the Modified, Shared and Invalid states are taken into consideration all implanting the MSI protocol. When a process is signified as it may neither read nor write, it then has a block in the Invalid or I state. Implicitly, a block is considered to be in the invalid state in the cache when it is not found in the cache. When a processor can read the block, but cannot write it, it's then considered to be in the Shared or S state. The Modified state or M state of a processor indicates that a processor can both read and write the block. To directly implement the coherence invariant, the three states of (Invalid, Shared, and Modified) are used through (a) permit only one processor at a time to be in the Modified state, and (b) forbid all other processors to be in the Shared state when one processor is in the Modified state at a certain point in time [11].

Replacing or victimizing occurs when a processor must evict a block currently held in the cache when demanding a new block. Two factors impact on the effort needed to evict a block; the coherence state of the block and the specific protocol. e.g. while evicting blocks in the Modified state, most protocols demand a data writeback to memory and permit a discrete eviction in the Shared state. If a protocol permits a

processor to evict blocks in the Shared state without sending a message, it is then considered to support silent evictions. If protocols require sending a notification message (although not the entire block) to the upper memory level in the Shared state, then they do not support silent eviction.

Much like the Shared state, the optional Owned or O state in a processor's cache allows read-only access to the block, while indicating that the main memory's value is incoherent or old. Hence; before evicting a block, the processor in the Owned state must update the upper memory level. Only one processor at a time is permitted to be in the Owned state, just like the modified state. Other processors, though, are permitted to be in the Shared state when one processor is in the Owned state unlike the Owned state [11].

Subtending the owned state provides two main advantages:

- First: Reducing system traffic hence, the Owned state does not ordain a processor while transitioning from Modified to Shared when in a read request to update memory. A protocol, not including the Owned state, requires the responder to provide data to the requester and updating memory (illustrated in Table 2.1) when transitioning from Modified to Shared. The addition of the Owned state permits a processor to transit from Modified to Owned state without sending a message to the memory at that time (illustrated in Table 2.1). A reduction of memory traffic occurs if another processor issues a write request for the block before it is evicted from the Owned processor's cache.

- Second: in some protocols (e.g., systems based on IBM's NorthStar/Pulsar processors) a

processor can respond more quickly by providing data from its SRAM cache than the

home memory controller can respond from its DRAM. In order to enable this

enhancement, a suitable mechanism for selecting a single responder is provided by

giving the processor in the Owned state the farther responsibility of responding to requests for data. On the other hand, a response from memory in other protocols (e.g., most directory protocols) is considerably faster than providing data from an Owned copy. The Owned state is not applied in these systems (preferring less latency for additional traffic).

The last state is the Exclusive or E state. The Exclusive state and the Modified state have many similarities, but differ in that the Exclusive state implies the contents of memory match the contents of the exclusive block. As a result to differentiating between the clean Exclusive state and its corresponding Modified dirty state, the need to update the block at the home memory when a block is evicted in Exclusive is eliminated. The memory responds to a read request with a clean-data response as long as there is no other processor caching the block. The duty of updating the memory is removed when the requesting processor transitions to Exclusive, granting it read/write permission to the block. By silently transitioning from Exclusive to Modified (demanding a writeback upon subsequent eviction), the block is then written fast without an external coherence request. Figure 2.3 illustrates the basic operations of MOESI states.

Figure 2.3 The basic operations of MOESI states.

**Table 2.1 MOESI State Transitions**

|             | State            | Modified (M)          | Exclusive<br>(E)       | Owned<br>(O)              | Shared<br>(S)             | Invalid<br>(I)                                                            |

|-------------|------------------|-----------------------|------------------------|---------------------------|---------------------------|---------------------------------------------------------------------------|

| tion        | Load             | Hit                   | Hit                    | Hit                       | Hit                       | Read request (response: Shared) →Shared  OR (response: clean)  →Exclusive |

| Core Action | Store            | Hit                   | Hit<br>→Modified       | Write request  → Modified | Write request  → Modified | Write request  → Modified                                                 |

|             | Eviction         | Writeback<br>→Invalid | Silent evict  →Invalid | Writeback<br>→Invalid     | Silent evict<br>→Invalid  | None                                                                      |

| Incoming    | Read<br>Request  | Send data  →Owned     | Send data  →Shared     | Send data                 | None                      | None                                                                      |

|             | Write<br>Request | Send data  →Invalid   | Send data  →Invalid    | Send data<br>→Invalid     | None<br>→Invalid          | None                                                                      |

#### 2.3.3 Hardware Protocols

Hardware protocols are divided into two primary groups: Snoop Bus Mechanism & Directory Based Method. Token protocol is also considered as another efficient protocol implemented by Milo M. K. Martin [11] for multiprocessor. Chapter 4, 5 and 6 JA JANIA SA describe these methods in further details.

## 2.3.3.1 Snoop Bus Protocols

Snooping protocols obtain coherence depending on a shared bus between the processors. On a processor write, the write is passed to the main memory via a bus passing through the cache. Updating or invalidating the cache entry appropriately is possible to any processor caching the address. Although, the Snooping protocols' disadvantage is that they are incapable of scaling well beyond 32 processors due to the shared bus.

The transactions in this method are observed and all memory write operations are monitored by a bus watcher unit built-in each processor/cache. (CH4 describe Snooping protocols in More Details).

## 2.3.3.2 Directory-Based Protocols

Unlike snoopy based protocols Directory based protocols do not exchange coherence information using a shared bus. Directory based protocols are of better scalability (might posses hundreds of cores per chip). According to this method, each core might obtain its own memory and, for efficiency, generally weak consistency is applied.

Systems of point-to-point unordered networks usually implement directory-based cache coherence protocols. Although cache miss latencies may be increased by these protocols as they propose indirection to import coherence information from the directory (usually on chip as a directory cache). Chapter four describes Directory protocols in More Details.

#### 2.3.3.3 Token Protocols

Token based protocols are assumed to combine the best features of both snooping and directory protocols: low-latency cache to cache misses and not depending on totally-ordered interconnects. Token Coherence [12] is a framework suggested in order to facilitate the development of token based cache coherence protocols. Three components comprise the Token Coherence: the *taken counting mechanism*; assuring the coherent reading and writing of data. The *persistent request mechanism*; solves protocol races and prevents starvation. These two mechanisms form the correctness foundation in order to assure correct operation in the different cases. On the other hand, the third component, which is *Performance policy*, is used to make the protocol fast and bandwidth efficient. More details about Token Protocol are discussed in chapter four.

#### 2.3.4 Compiler and Software protocols

Software protocols impose consistency with limited hardware support depending on the compiler or specialized software handlers. They are somewhat comparable to Distributed Shared Memory (DSM) systems but a lower level such as: sharing, usually in blocks not pages, the need for more efficiency to obtain better performance and architecture support for sharing. We just focus on the hardware coherence protocols.

Software protocols can be classified in accordance to many criteria[45]. The most important criteria are:

- **Dynamism**: compile-time or run-time analysis

- Selectivity: level of coherence actions

- KUniversity Restrictiveness: conservative or as-needed consistency enforcement

- Adaptivity: can protocol adapt to access patterns

- Granularity: coherence data size and structure

- Blocking: program block on which coherence is enforced

- Positioning: position of coherence instructions

- Updating: how memory is updated after a write

- Checking: how incoherence is detected

## 2.3.4.1 Software Coherence with Limited Hardware Support

According to this approach, a consistency code must be generated by the compiler for, there is no hardware coherence provided. Time tags are kept in the hardware and are updated on every write. In order to ensure data consistency, the compiler while on a read generates coherence read that screens time tags. The hardware's duty is to preserve tags while it's the compiler's duty to detect inconsistent reads. Using tags, also allows for performing dynamic self-invalidation of blocks. A number of techniques are based on using these time tags.

Petersen and Li have developed a special algorithm if the hardware has no time tag, as it only uses page translation hardware and page statues table [112]. According to this algorithm, a page handler at the page-level is in charge of maintaining the sharing of information. In the case of page access or fault, the sharing of information, updating page table and performing coherence actions is the software handler's duty. Software

handlers are slower than hardware for they are limited by the memory access paths and bound to the OS [45].

#### 2.3.4.2 Enforcing coherence by Restricting Parallelism

Structuring the language, in order to limit parallelism, is another way compilers use to assure coherence. Using this method, enforce coherence are easier to enforce. Moreover; a limit is forced upon the programmer and potential parallelism. However; no hardware support is needed to attain well performance and it simplifies the compiler design. Do all parallel loops, as well as, master/slave processes are contents of parallel language restrictions[45].

## 2.3.4.3 Optimizing Compilers

Optimizing compilers are designed in order to maintain coherence of limited hardware support, and at the same time, not limiting the programmer too much. Thus, depending on detecting data dependencies, probably using synchronization variables (locks, barriers), might provide hints to the hardware, able to detect the need for coherence, dynamic sharing problems are also probable. Overall; providing good performance, but difficult to design [45].

### 2.4 Literature Review and Related work

This section presents some related work on existing cache coherence techniques.

The scope and the amount of related work are large, so we focus on the aspects most fundamental and related to the research in this thesis.

Snooping coherence on a bus was first described by Goodman [56]. Early bus implementations used electrically shared wires that held the bus for an entire coherence

transaction. But more modern snooping systems implement a logical bus using additional switches, state, and logic rather than shared electrical wires.

Barroso et al. [113] examined snooping on a ring and proposed an approach that Michael Marty [111] generalize and call greedy snooping. The primary commercial systems using ring-based coherence, the IBM Power4/5, also uses a greedy-like snooping protocol for coherence on a ring [114]. A greedy snooping protocol broadcasts coherence requests to all other nodes in the system. While a ring naturally accomplishes the broadcast operation, there is no total ordering or atomicity. Therefore, unlike the bus protocol, a requestor cannot be assured that its coherence request is ordered once the message is transmitted and racing (or conflicting) coherence requests must be handled differently.

A directory protocol contains state about the sharing status of a given block to determine the actions needed when a coherence request is received. A typical directory includes a list of sharers for each block, and a field that points to the current owner. A directory can also take other forms, such as a linked list of sharers [101], or sharing lists at a coarser granularity than single processor-cache nodes [98]. Directory-based cache coherence was first suggested by Tang [85] and Censier et al. [84]. Examples of commercial machines using directories include the SGI Origin [17] and the Alpha 21364 [67].

The previous techniques to coherence, snooping and directory, both require the careful coordination of message exchanges and of state-machine transitions to ensure the coherence invariant. The properties of the interconnect also further complicate the design of the protocol to ensure the invariant. A technique proposed in 2003, token coherence, directly enforces the coherence invariant through a simple technique of counting and exchanging tokens.

Token coherence [12] associates a fixed number of tokens with each block. In order to write a block, a processor must acquire all the tokens. To read a block, only a single token is needed. In this way, the coherence invariant is directly enforced by counting and exchanging tokens. Cache tags and messages encode the number of tokens using Log2N bits, where N is the fixed number of tokens for each block.

Token coherence enables a broadcast protocol on an unordered interconnect as well as others described in Martin's thesis [11]. The TokenB broadcast protocol has some similarities to the greedy snooping approach and a few key differences. In TokenB, coherence requests are broadcast directly from the requesting processor to all other processors like greedy snooping. Unlike greedy snooping, only processors sharing the block must respond with an acknowledgement message. However in TokenB, conflict is not explicitly detected because a snoop response is not received from every processor. Therefore, TokenB uses a per-request timer that is used to issue retries or to invoke a persistent request upon timeout.

Many work have been done through the last years to evaluate and propose an efficient cache coherence protocols; but no one model the Snooping, Directory, and Token protocols on the multicore architecture and evaluate them using meaningful performance metrics as we did in this thesis.

## **Chapter 3 Evaluation Methodology**

The objective of evaluation is to explain the relative behavior of different coherence protocols (traditional protocols and Token Coherence based protocols). We aim not to (1) Generate ultimate execution times or throughput rates for our simulated systems or (2) Evaluating such protocols on all of the future's system configurations. We use an approximation of a chip multiprocessor system in order to accurately obtain relative comparisons and evaluations instead. Full system simulation and modeling of the first-order timing effects for approximating an aggressive multicore system operating commercial loads are the means to reach such an aim. Our goal is to get the first-order effects, although —similar to most architectural simulations— Capturing all system's aspects in precise detail is not what we try to do.

## 3.1 Simulation Tools

In order to evaluate the demand system; full-system simulation is used. Using full system simulation allows for evaluating the proposed systems when running realistic scientific applications on top of actual operating systems. As well as capturing the subtle timing effect that can't be captured with trace-based evaluation.

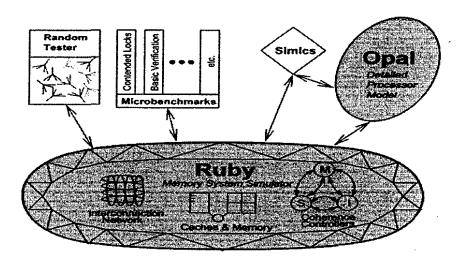

The Simics full-system multiprocessor simulator [46] extended with the Wisconsin GEMS simulation environment [47] is used in order to perform the analysis. Simics is a system-level architectural simulator developed by Virtutech AB [46] with the ability to operate unmodified commercial applications and operating systems. Simics only provides an interface equipped by GEMS as to support the memory hierarchy model. GEMS is a set of modules that extends Simics with timing fidelity. Two primary modules make up GEMS: Ruby and Opal. Ruby models memory hierarchies and uses the SLICC domain-specific language to specify protocols. Opal

models the timing of an out-of-order SPARC processor. The relation between the Simics simulator and GEMS toolset is illustrated in Figure 3.1.

### 3.1.1 Simics Simulator

An overview of the simulation tools used is illustrated in Figure 3.1. Simics is found on the top. Simics is defined as a full functional system simulator enabling the booting of an unmodified operating system thus in order to execute actual applications.

Figure 3.1 A view of the GEMS architecture with simics simulator [47].

A simple in-order processor is modeled in Simics. Simics uses Ruby in order to pass all the load and store instructions and the instruction fetch requests. Determines, if the operation hits or misses, thus by performing the cache access. In the case of a hit, instructions are executed normally by Simics. But in the case of a stall, Ruby simulates a cache miss only after stalling Simics' request from the issuing processor. The request completion is determined by contention, latency of messages, and other factors. Ruby determines the timing-dependent functional simulations in Simics by controlling Simics' advancing time.

## 3.1.2 Ruby Module

Ruby is found under Simics, as it is a module used to protocol-independent components (cache arrays, memory arrays, message buffers, and assorted glue logic) as well as protocol-dependent components (cache controllers and memory controllers).

To simulate timing, Ruby takes on a queue-driven event model. Message buffers are in charge of communicating cache controllers and memory controllers. The recipient is scheduled to wake up as soon as the next message becomes available to read from the buffer.

Ruby solves the miss in the case of a cache miss by generating the events required by the implemented protocol. When an exchange of messages is implied by an event through the network, the messages are stalled in the message buffers and their transmissions are simulated in details in the network simulator upon their arrival. A wake up is scheduled as soon as the message arrives to the recipient component.

## 3.2 Performance Metrics

Throughout this research, we demonstrate how the overall performance of our proposals by the runtime i.e. measuring the time necessary to complete certain amount of work. The metric instructions-per-cycle has been used by other works instead of runtime in judging performance improvements. However; system timing effects of multiprocessor workloads may alter the number of instructions executed therefore, Instruction Per Cycle (IPC) is not a suitable metric for evaluating the coherence protocols and systems. Thus the performance of the system is not guaranteed to be reflected by measuring IPC and running the simulator for a specific number of instructions [48]. This is due to the magnificence of the variation in the instruction path of multithreading workloads that run on multiple processors.

Runtime is used to conclude that "protocol A is X % faster than protocol B" using the formula:

$$X = \left(\frac{\text{runtime(B)}}{\text{runtime(A)}} - 1.0\right) * 100.$$

Equation #1

The measurement is started at the parallel phase so that we avoid measuring thread forking. Until now, a full system checkpoint (to provide a well-defined starting point) is used to initialize the system state and to simulate the execution until the end of the parallel phase. The number of cycles is recorded and referred to as application time in order to complete the parallel phase.

Endpoint traffic (in messages per miss) and interconnect traffic (in terms of bytes on interconnect links per miss) are other ways besides reporting runtime that measure and report the traffic. The endpoint traffic shows the amount of controller bandwidth needed for handling incoming messages. The amount of link bandwidth used by the messages are indicated in the interconnect traffic as they traverse the interconnection.

The last metric is mostly not bound to the particular interconnect and message size. On the contrary, the interconnect topology, the use of bandwidth-efficient multicast routing, and message size are what influence the last metric.

Due to the computational intensity of detailed architectural timing simulations, we are limited to simulating only a short segment of the workload's entire execution. Two techniques are used to subdue such limitations and partially overcoming this problem. At the beginning, system cold-start effects are avoided by warming up and check pointing all workloads, and restoring the cache contents captured as to assure the warming of caches all as part of our checkpoint creation process. Second, the approach of simulating each design point a number of times as to address the variability in commercial loads, this is done by small, pseudo-random perturbations of request latencies [49, 50]. These perturbations cause alternative operating system scheduling

paths in deterministic simulations. A distribution of runtimes is created by operating many of these pseudo-randomly perturbed systems. The reduction of the effect of the skewed nature of the distribution is possible by eliminating all data points beyond 1.5 standard deviation from the mean. Error bars in our runtime results approximate a 95% confidence interval centered on the arithmetic mean of the remaining data points.[11] Every data point is approximately the aggregate of 5 to 15 data points; a large number of simulations are used for configurations and workloads exhibiting the most variation.

## 3.3 Workload Descriptions

We used three multi-threaded commercial workloads from the Wisconsin Commercial Workload Suite [49]: an online transaction processing workload (OLTP), a Java middleware workload (SPECjbb), and a static web serving workload (Apache). The previously mentioned workloads operate on a simulated 16-core SPARC processor that runs Solaris 9. The simulated system has 4GBs of main memory.

Online Transaction Processing (OLTP): The OLTP workload is built on a TPC-C v3.0 benchmark with 16 users/processor and no think time. IBM's DB2 v7.2 EEE database management system formalizes the back-end and is responsible for almost all of the activities in this workload. The users query a 5GB database with 25,000 warehouses stored on eight raw fiber-channel disks. The database logic is also stored on the disk. The system is warmed up with 100,000 transactions and the hardware caches are warmed up with additional 500 transactions.

Java Server Workload: SPECjbb. SPECjbb2000 is a server-side Java benchmark modeling a 3-tier system, its primary focus is on the middleware server business logic. Sun's HotSpot 1.4.0 Server JVM drives the benchmark. The experiments use 1.5 threads

and 1.5 warehouses per processor. However; we use over a million transactions to warm up the system and 100,000 transactions to warm up simulated hardware caches.

Static Web Content Serving: Apache. Apache 2.0.43 configured is used as to obtain a hybrid multi-process multi-threaded server model with 64 POSIX threads per server process. The web server is SURGE driven with 3200 simulated clients each with a 25ms think time between requests. Apache logging is disabled to maximize server performance. We use 800,000 requests to warm up the system and 1000 requests to warm up simulated hardware caches.

# 3.4 Modeling a CMP with Simics/GEMS

This section is dedicated to describing how GEMs are used to model CMP memory systems in this thesis. Like most simulation, some components are realistically modeled and some idealized. Our goal in this evaluation is to validate designs and to give insights into the relative merits of a subsystem studied and not to simulate realistic or absolute runtimes for all future CMPs.

We aim to capture first-order effects of coherence protocols, such as all the messages needed in order to implement the protocol at certain interconnect. Most of the idealized components of the simulator are expected to impact on all protocols in the same way, or else the designer has to compensate the design dependant subsystems in order for them to match the given protocol. e.g., if a protocol requires that a cache snoop X tags/cycle, then the designers would engineer this ability into the implementation. Whenever necessary; these events are measured and their counts are reported even if they do not affect the simulated runtime.

At first, many controllers are connected via networks in a specific topology as to formalize the CMP memory model. L1 Caches interface processor models. After that L1 caches interact with other controllers (i.e., directory/memory controller) and model the timing of an L1 miss by interconnecting links. Timing is usually modeled by a controller that specifies the delay when a message is injected into the network, and delay incurred by modeling the delivery of the message.

Following are details of how the main components of the system are modeled:

## 3.4.1 Simulated System

A multicore server is simulated while running commercial workloads and using multiple interconnects and coherence protocols thus, evaluate Cache Coherence Protocols. The system we target is a 16-core processor SPARC v9 system with highly integrated nodes each including a dynamically-scheduled processor, split first level instruction and data caches, unified second level cache, coherence protocol controllers, and a memory controller for part of the globally shared memory. Sequential consistency is implemented in the system by using invalidation-based cache coherence and an aggressive, speculative processor implementation [51, 52].

We select a variety of coherence protocols, system interconnects, latencies, bandwidths, cache sizes, and other structure sizes. The parameters for the memory system and the processors are listed in Table 3.1. We limit the bandwidth of memory controllers and cache controllers; which limit the bandwidth that is caused by external requests for the DRAM, cache tag arrays, and cache data arrays indirectly. We also apply simulation both with unbounded interconnect link bandwidth and interconnects with 4GB/sec links. By these two types of simulations, we are able to distinguish between changes in uncontained latency and changes in latency due to interconnect bandwidth constraints.

**Table 3.1 Simulation Parameters**

| Coherent Memory System Parameters |                                                                                                            |  |  |  |

|-----------------------------------|------------------------------------------------------------------------------------------------------------|--|--|--|

| Private L1 Caches                 | Split I&D, 64 KB 4-way set associative, 64-byte line, 1ns latency                                          |  |  |  |

|                                   | (2 cycles)                                                                                                 |  |  |  |

| L2 unified cache                  | 4MB, 6ns latency (12 cycles)                                                                               |  |  |  |

| size and latency                  | initial, one money (12 dyers)                                                                              |  |  |  |

| main memory size                  | 4GB, 80ns (160 cycles)                                                                                     |  |  |  |

| and latency                       | 102, como (100 es cita)                                                                                    |  |  |  |

| interconnect link                 | 4GB/second or unbounded bandwidth 15ns latency (30 cycles)                                                 |  |  |  |

|                                   | Calculated Average Miss Latencies                                                                          |  |  |  |

| Interconnect hop                  | 68ns (136 cycles)                                                                                          |  |  |  |

| memory-to-cache                   | $= L2 \text{ miss}(6) + 2 \text{ hops}(2 \times 68) + \text{mem}(80) = 222 \text{ns} (444 \text{ cycles})$ |  |  |  |

| direct cache-to-cache             | = L2 miss + 2 hops + cache(6) = 148ns (296 cycles)                                                         |  |  |  |

| indirect cache-to-                | = L2 miss + 3 hops + directory(DRAM=80,SRAM=6) + cache                                                     |  |  |  |

| :                                 | DRAM directory = 296ns (592 cycles)                                                                        |  |  |  |

| cache                             | SRAM directory = 222ns (444 cycles)                                                                        |  |  |  |

After that, we describe the coherence protocols and system interconnection:

#### 3.4.2 Coherence Protocols

Using a few distinct MOESI coherence protocols the simulated systems are compared. The migratory sharing optimization [11], is applied to protocols to improve their performance, the upgrade requests are not supported by any protocols. Coherence is kept at on aligned 64-byte blocks. All request, acknowledgment, invalidation, and dataless token messages are of the size 8-bytes (including the 40+ bit physical address and token count whenever necessary); data messages include the 8-byte header and the

64 bytes of data. These message sizes do not include any extra bits used by the interconnect to detect and correct bit errors. Three main protocols are used: Snooping (an aggressive snooping protocol described in Section 2.3.3.1), Directory (a traditional directory protocol described in Section 2.3.3.2), and Token (an optimized version of a protocol that migrate and improve Snooping and directory protocols described in Section 2.3.3.3).

### 3.4.3 System Interconnects

The same GEMS' are used in the networking model as to approximate all of the target interconnection networks. For each target CMP, a specific network topology is specified using a configuration file. The links between network switches and the endpoints of the interconnect are determined by the file. Fix latency and bandwidth parameters are the specifications of each link since GEMS does not model the characteristics of links at the lower network levels. The latency specified and other queuing delay resulting from insufficient bandwidth, are always incurred in a message.

Whenever convenient, the following chapters will elaborate each of the previous components and evaluations in specified details.

## **Chapter 4 Cache Coherence Protocols**

In this chapter, we describe the traditional protocols (Snooping based protocols and Directory based protocols) in addition to the Token coherence protocol: how they are working and what the advantages and disadvantages of each of them are and how the improvement of these protocols can be done, and in the last section we describe the output raw simulations results.

## 4.1 Snooping Protocols

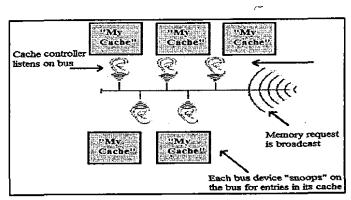

Snooping protocols are mainly focused on observing bus activities and carrying out the appropriate coherency commands [53]. The bus shows all writes and read misses. Global memory is moved in blocks, a state is dedicated to each block thus determining what happens to the entire contents of the block [54]. Figure 4.1 shows the snooping process.

Figure 4.1 Snooping Process.

The reliance of snooping protocols on a "bus" or "virtual bus" interconnect are the primary properties that differentiate snooping protocols from other protocols. Former multichip processors connected all cores and memory modules in the system by a shared-wire, multi-drop bus. Snooping protocols make use of such bus-based

interconnects depending on two bus properties: (1) the visibility of all requests that appear on the bus are to all components connected to the bus (cores and memory modules), and (2) the visibility of all requests to all components by a similar total order (the order in which they gained access to the bus) [55]. Essentially, low-cost atomic broadcast of requests is provided by a bus.